Intel PowerVia – pierwsze testy zasilania chipów „od spodu” wypadły pomyślnie

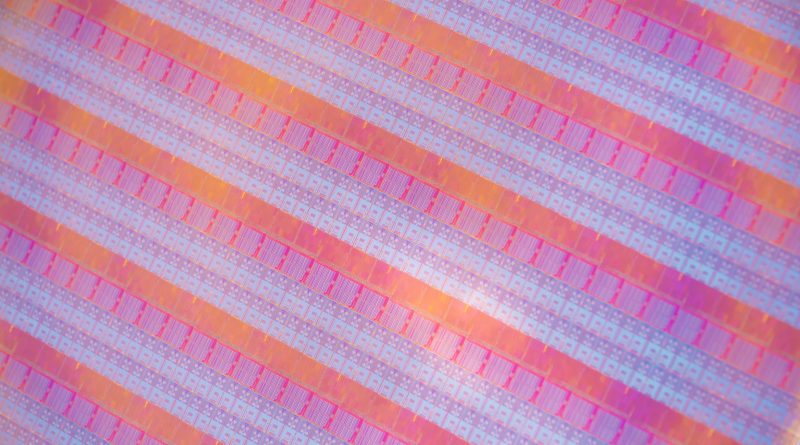

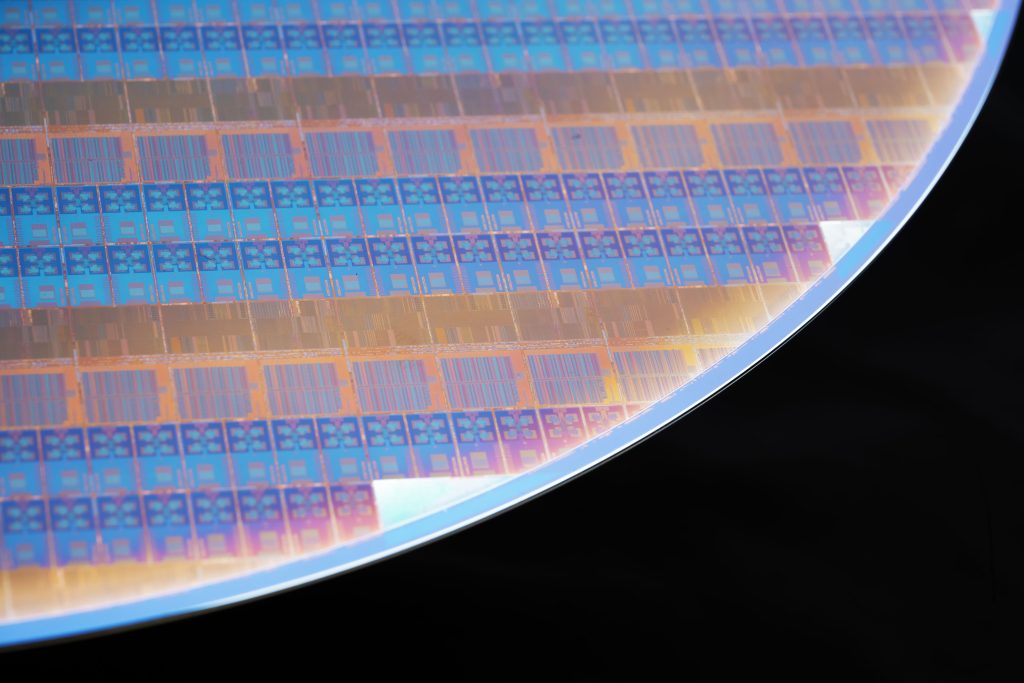

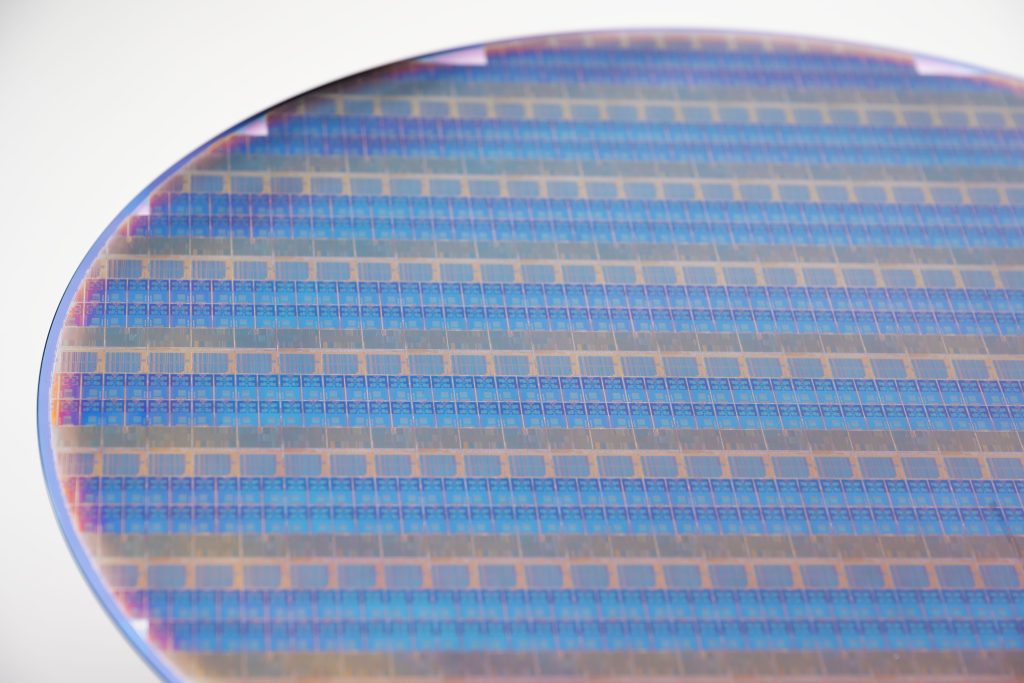

Intel w testowym układzie wprowadza PowerVia – czyli zasilanie chipów za pomocą backside power delivery (zasilanie od tyłu/spodu). Technologia ta pojawi się w układach produkowanych w węźle procesowym Intel 20A w pierwszej połowie 2024 roku i ma rozwiązać problem konkurowania o przestrzeń dla linii zasilania i sygnałowych na jednej płaszczyźnie chipa.

PowerVia to ważny kamień milowy w naszej agresywnej strategii „pięć węzłów w cztery lata” i na drodze do osiągnięcia biliona tranzystorów w pakiecie do roku 2030. Wykorzystanie wersji próbnej węzła procesowego i testowego układu umożliwiło nam zminimalizowanie ryzyka związanego z backside power delivery dla naszych wiodących węzłów procesowych, co umieszcza Intela o krok przed konkurentami we wprowadzaniu tej technologii na rynek – mówi Ben Sell, wiceprezes ds. rozwoju technologicznego w firmie Intel

Niebiescy oddzielili rozwój PowerVia od samych układów, aby mieć pewność, że uda się zastosować tę technologię w węzłach procesowych 20A i 18A (odpowiednio 2 i 1,8 nm). Jak dowiodły testy, backside power delivery umożliwia niezwykle efektywne wykorzystanie zasobów ze wskaźnikiem wykorzystania komórek większym niż 90% oraz skalowaniem tranzystorów, co pozwala projektantom układów osiągać wzrost wydajności i efektywności w swoich produktach. Firma przedstawi te wyniki w dwóch artykułach podczas sympozjum VLSI, które odbędzie się w dniach 11-16 czerwca w Kioto w Japonii.

Intel PowerVia umożliwi większe upakowanie tranzystorów

Rosnąca liczba zastosowań, w tym sztuczna inteligencja i grafika, wymagają mniejszych, gęściej upakowanych oraz potężniejszych tranzystorów, aby sprostać wymaganiom obliczeniowym. Jak przez wiele dekad, tak i obecnie, linie zasilania oraz sygnałowe w chipach konkurują ze sobą, a oddzielenie tych dwóch elementów pozwoli na zwiększenie wydajności i efektywności energetycznej. Technologia backside power delivery jest niezbędna dla skalowania układów i umożliwi projektantom zagęszczenie tranzystorów bez poświęcania innych zasobów.

Testowy układ wykorzystuje również reguły projektowania dostosowane do litografii EUV (extreme ultraviolet lithography – litografia w ekstremalnym ultrafiolecie), która umożliwia zmniejszenie powierzchni układu i obniżenie kosztów. Potwierdziły się też przewidywane charakterystyki termiczne chipa.

Źródło: Intel

Miłośnik nowoczesnych technologii, głównie nowych rozwiązań IT. Redaktor w czasopismach Gambler, Enter, PC Kurier, Telecom Forum, Secret Service, Click!, Komputer Świat Gry, Play, GameRanking. Wiele lat spędził w branży tłumaczeniowej – głównie gier i programów użytkowych. W wolnych chwilach lata szybowcem, jeździ na rowerze i pochłania duże ilości książek.