Intel ogłasza Tera-Scale Computing Research Program

Podczas pierwszego spotkania z dziennikarzami w ramach rozpoczynającego się właśnie Intel Developer Forum Justin Rattner, dyrektor ds. technologii (CTO) w firmie Intel, zapowiedział nadejście nowego rozdziału w historii komputerów: ery „tera” („The Era of Tera”). Moc komputerów rośnie w bardzo dynamicznym tempie, a nośniki danych są coraz pojemniejsze i coraz tańsze. Dochodzimy do sytuacji, gdy nasze komputery udostępniać będą pamięci masowe liczone w terabajtach i procesory o wydajności liczonej w teraflopach. Obecnie wykorzystywane technologie nie są w stanie efektywnie i ekonomicznie przetwarzać tak duże ilości danych.

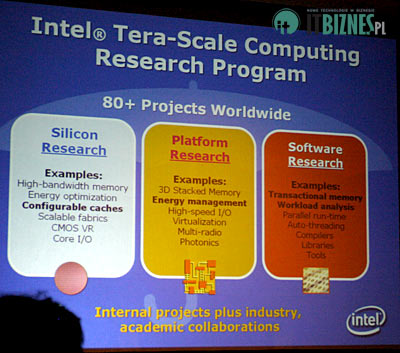

Intel ogłasza zatem utworzenie programu Tera-Scale Computing Research Program, w ramach którego ponad 1100 naukowców w 18 placówkach na całym świecie opracowywać będzie nowe technologie, które umożliwią dalsze posuwanie rynku IT na przód. Badacze pracują nad nowymi technologiami produkcji, nowymi mikroprocesorami czy nowymi systemami komunikacyjnymi.

Justin Rattner

Z punktu widzenia Intela, największego producenta procesorów na świecie, problemem jest nie tylko zwiększenie mocy CPU, ale także obniżenie poboru energii. Rattner zapowiedział, że już w najbliższych latach ujrzymy procesory o dziesiątkach, a nawet setkach rdzeni, które pobierać będą mniej energii niż produkowane obecnie procesory jednordzeniowe.

Dla producenta procesorów problemem nie jest zbudowanie ukladu o dziesiątkach rdzeni. Kłopot stanowi optymalne połączenie tych rdzeni ze sobą, tak by każdy z każdym mógł się bezproblemowo komunikować. Dodatkowo wąskim gardłem jest wciąż niewystarczająca przepustowość pamięci. I wreszcie problem chyba najważniejszy: niewielka liczba odpowiednich aplikacji, które są w stanie wykorzystać pełnię możliwości procesorów wielordzeniowych.

Inżynierowie Intela pracują nad rozwiązaniem tych problemów. W ramach 80 projektów składających się na Tera-Scale Computing Research Program opracowują pamięć nowej generacji o niezwykle wysokiej przepustowości, nowe typy interfejsów I/O, specyfikację konfigurowalnej pamięci podręcznej, a także specjalne aplikacje dla programistów, które analizować będą kod programów i automatycznie go zrównoleglać (rozbijać na wątki), nawet jeśli kod jest typowo sekwencyjny. Badacze z Intela przygotowują specjalne kompilatory i biblioteki dla programistów, tak by ci mogli w pełni wykorzystać moc procesorów o dziesiątkach czy setkach rdzeni. Wrac z coraz większym upowszechnianiem się procesorów dwu, cztero- i więcej rdzeniowych spodziewać się możemy zatem coraz większej popularności aplikacji wielowątkowch.

Rattner zaprezentował przykład rozwiązania jednego z powszechnych problemów, blokowania pamięci przez kilka jednocześnie działających procesów, co doprowadza do ich zakleszczenia (dead-lock). Intel zaproponował wykorzystanie pamięci transakcyjnej, wykorzystującej technologię koordykowania tego, jak wątki uzyskują dostęp do pamięci. Konflikty przy dostępie do pamięci wykrywane i rozwiązywane będą już na poziomie sprzętu, co znacznie zwiększy wydajność aplikacji, ale także ułatwi pisanie programistom kodu. Rattner pokazał demo aplikacji, która dzięki wykorzystaniu pamięci transakcyjnej przyspieszyła o 60%, chociaż – jak stwierdził – możliwe jest uzyskanie nawet 3-4-krotnego wzrostu wydajności.

Dziennikarz komputerowy od 1994 roku. Właściciel i redaktor naczelny portalu ITbiznes; prowadzący magazyn ITbiznes na antenie kanału telewizyjnego Biznes24; gospodarz programu poradnikowego „Cyfrowy Niezbędnik” na antenie kanału telewizyjnego Antena HD; gospodarz podcastów Elektrycznie Tematyczni o samochodach elektrycznych oraz Zrozumieć AI o sztucznej inteligencji. Współprowadzący podcast ITbiznes o technologiach w biznesie. Twórca bloga o pasjach Fabryka Pasji. Założyciel, redaktor naczelny i były właściciel portalu PCLab.pl. Założyciel i były redaktor naczelny serwisów AGDLab.pl, Softonet.pl. Były redaktor naczelny serwisów PC.com.pl i Technowinki.onet.pl.